MachXO2 a tři LEDky

V předchozím článku jsme vytvořili první projekt v Lattice Diamond a umíme rozblikat LEDku. VHDL kód, který LEDkou bliká, spadl odněkud z nebe, chtělo by to nějaké vysvětlení. V tomto článku doplníme informace a navíc přidáme dvě LEDky, které budou blikat s vyšší frekvencí.

Jak to vlastně bliká

Máme sice k dispozici zdroj 50 MHz pulsů, ale když takovou vysokou frekvencí budeme blikat LEDkou, bude to vypadat, že jenom svítí. Musíme získat nižší frekvenci. Jak na to? Budeme kmitočet dělit. Budeme kmitočet postupně půlit tak dlouho, až dostaneme frekvenci, jejíž změny můžeme očima postřehnout.

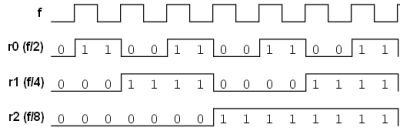

Graf půlení frekvence

Myšlenka je to úžasná, ale jak to uděláme v tom FPGA? Uděláme si binární čítač. Vytvoříme si registr, dostatečně široký, tedy s dostatečným počtem bitů a při každé změně signálu clk z hodnoty 0 (nula) na hodnotu 1 (jedna) registr inkrementujeme, čili přičteme k němu jedničku. Na obrázku vidíte, jak se při frekvenci f hodinového signálu clk mění obsah tří nejnižších bitů našeho regitstru. Frekvence změn obsahu nejnižšího bitu r0 je poloviční oproti frekvenci signálu clk, frekvence změn bitu r1 je čtvrtinová a u bitu r2 je to osmina. A tak to půjde pořád dál. Pokud budeme mít dost bitů, můžeme čekat na bliknutí třeba celý den. Kdo by ale čekal tak dlouho. Jakou šířku registru ale zvolit? Pomůže nám tabulka a hned bude jasno.

| bit | f [Hz] | T [ms] |

| 50 000 000,000 | 0,00002 | |

| 0 | 25 000 000,000 | 0,00004 |

| 1 | 12 500 000,000 | 0,00008 |

| 2 | 6 250 000,000 | 0,00016 |

| 3 | 3 125 000,000 | 0,00032 |

| 4 | 1 562 500,000 | 0,00064 |

| 5 | 781 250,000 | 0,00128 |

| 6 | 390 625,000 | 0,00256 |

| 7 | 195 312,500 | 0,00512 |

| 8 | 97 656,250 | 0,01024 |

| 9 | 48 828,125 | 0,02048 |

| 10 | 24 414,063 | 0,04096 |

| 11 | 12 207,031 | 0,08192 |

| 12 | 6 103,516 | 0,16384 |

| 13 | 3 051,758 | 0,32768 |

| 14 | 1 525,879 | 0,65536 |

| 15 | 762,939 | 1,31072 |

| 16 | 381,470 | 2,62144 |

| 17 | 190,735 | 5,24288 |

| 18 | 95,367 | 10,48576 |

| 19 | 47,684 | 20,97152 |

| 20 | 23,842 | 41,94304 |

| 21 | 11,921 | 83,88608 |

| 22 | 5,960 | 167,77216 |

| 23 | 2,980 | 335,54432 |

| 24 | 1,490 | 671,08864 |

| 25 | 0,745 | 1342,17728 |

Tabulka půlení frekvence

V tabulce je přehledně zobrazeno, jak se na každém vyšším bitu čítače frekvence půlí a v druhém sloupci je vidět délka periody pulsů. Ta je zobrazena v milisekundách. Pokud budeme mít 26bitový registr (počítáme od nuly, máme bity 0 až 25, což je 26 bitů), tak se nám bude obsah nejvyššího bitu opakovat s periodou 1,342 sekundy neboli s frekvencí 0,745 Hz. Tak je to v příkladě z předchozího článku, kde jsme nadefinovali 26bitový vektor a obsah jeho nejvyššího bitu (25. bitu, počítáme je od nuly) přiřazením přenášíme na výstupní port led.

ARCHITECTURE blinker_arch OF blinker IS

SIGNAL counter : STD_LOGIC_VECTOR(25 DOWNTO 0);

BEGIN

PROCESS (clk) IS

BEGIN

IF (clk'EVENT AND clk='1') THEN

counter <= counter + 1;

END IF;

END PROCESS;

led <= counter(25);

END blinker_arch;

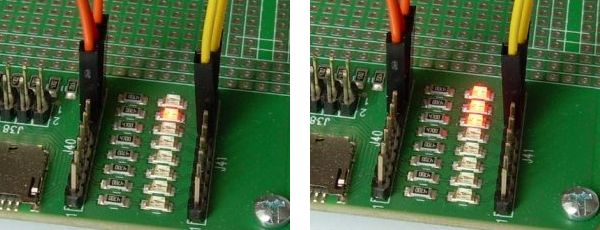

Na BaseBoardu je LEDek dostatek a tak zkusíme rozblikat ještě další dvě. Přivedeme na ně obsah dvou následujících nižších bitů 24 a 23. LEDky budou blikat s dvoj a čtyřnásobnou frekvencí a budou blikat synchronně. Tenhle dělič kmitočtu nám ještě dobře v budoucnu poslouží. Budeme ho používat pro naše další pokusy jako zdroj pulsů o různých frekvencích. Třeba pro 7segmentový displej.

Konec řečí, pokročme k činům. Podle postupu z předchozího článku vytvoříme nový projekt v Lattice Diamond. Upravíme zdrojový kód VHDL a přidáme další dva výstupní porty. Na ně vyvedeme obsah bitů 24 a 23 čítače.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY tled IS PORT(

clk : IN STD_LOGIC;

led1 : OUT STD_LOGIC;

led2 : OUT STD_LOGIC;

led3 : OUT STD_LOGIC);

END tled;

ARCHITECTURE tled_arch OF tled IS

SIGNAL counter : STD_LOGIC_VECTOR(25 DOWNTO 0);

BEGIN

PROCESS (clk) IS

BEGIN

IF (clk'EVENT AND clk='1') THEN

counter <= counter + 1;

END IF;

END PROCESS;

led1 <= counter(25);

led2 <= counter(24);

led3 <= counter(23);

END tled_arch;

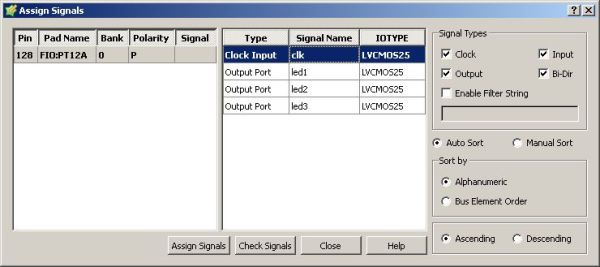

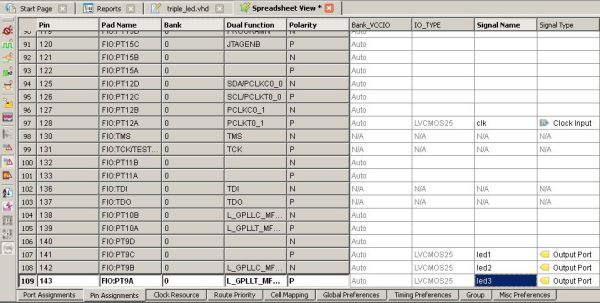

Po překladu a syntéze musíme připojit do vnějšího světa oproti předchozímu příkladu navíc výstupní porty pro dvě další LEDky.

Výstupní porty napojíme na piny vedle první LEDky, a to na piny číslo 142 (port PT9B) a číslo 143 (port PT9A). Takhle pak vypadá tabulka Pin Assignment.

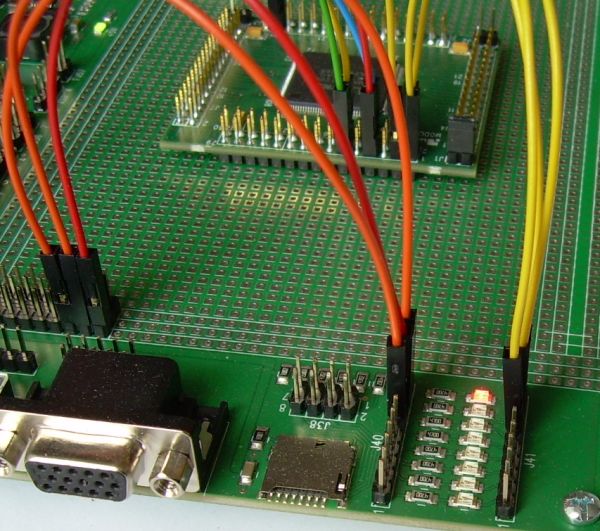

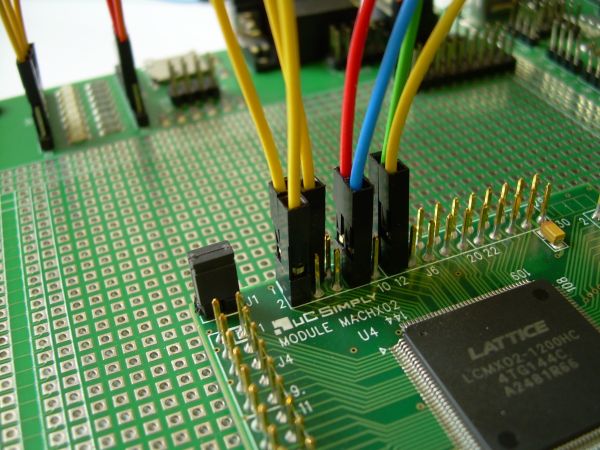

Ještě zbývá propojit kablíky vývody FPGA modulu s LEDkami na BaseBoardu. Na FPGA modulu jsou to piny číslo 1 a 2 na konektoru J6. Pin číslo 3 na konektoru J6 FPGA modulu už máme připojený na LEDku z předchozího příkladu.

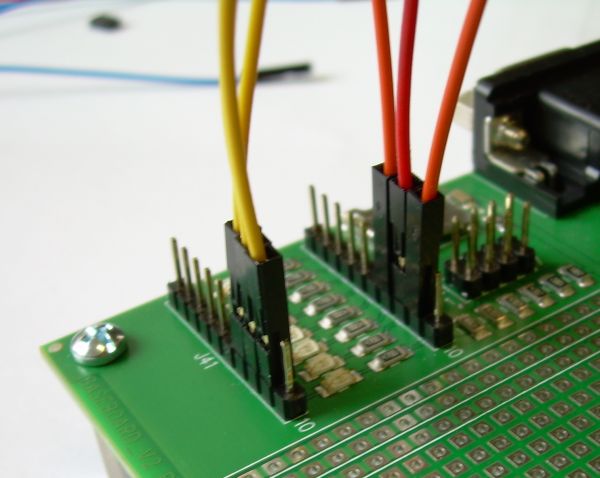

Na BaseBoardu jsme zvolili LEDky, které jsou hned vedle té zapojené a signály z FPGA jsme přívedli na jejich katody na pinech 8 a 7 na konektoru J41. To jsou ty žluté kablíky. Anody LEDek jsme červenými kablíky připojili na rozvod napájení 3,3V.

Všechna propojování provádíme při vypnutém napájení BaseBoardu! Až máme vše hotovo a aspoň desetkrát zkontrolováno, můžeme zapnout napájení BaseBoardu.

Vyexportujeme JEDEC nebo Bistream výstupní soubor s naším novým designem a naprogramujeme ho do FPGA. Ať už to bliká.